# *MONROBOT XI PROGRAM MANUAL*

Copyright 1960

Monroe Calculating Machine Company, Inc.

Orange, New Jersey

Form MO-96 ED 1-64

Printed in U.S.A.

WORKS OF JAMES W. THOMAS

## INTRODUCTION

The purpose of this manual is to acquaint the programmer and coder with the machine language of Monrobot Mark XI. The manual is written for those people who are experienced in the programming and coding of general purpose computers. It is assumed that most computer terms used here are familiar to the reader; terms that are specific to the Monrobot Mark XI are defined as they are introduced into the text.

No attempt has been made to provide either introductory comments about computers or methods of programming computers. For those people not experienced in programming, Monroe literature or some text on basic computer programming should be studied prior to reading and using this manual.

Other Monroe literature defines the specific techniques of numeric input and output, alphanumeric handling, multiplication and division, and program input/output.

The scope of this manual is believed sufficiently broad to enable people to program, code, and understand Monrobot Mark XI in a reasonably short period of time. Consequently, some of the more esoteric information about the computer has been omitted.

## TABLE OF CONTENTS

|                                           |    |

|-------------------------------------------|----|

| INTRODUCTION . . . . .                    | ii |

| GENERAL . . . . .                         | 1  |

| Input . . . . .                           | 1  |

| Output . . . . .                          | 1  |

| SEXADECIMAL SYSTEM . . . . .              | 3  |

| Tetrad Numbering . . . . .                | 4  |

| Conversion . . . . .                      | 4  |

| Instructions . . . . .                    | 6  |

| Monrobot Mark XI Commands . . . . .       | 8  |

| NUMBER SYSTEM . . . . .                   | 9  |

| Overflow . . . . .                        | 9  |

| STORAGE SYSTEM . . . . .                  | 10 |

| General Storage . . . . .                 | 10 |

| Access Time . . . . .                     | 11 |

| Fast Access Storage . . . . .             | 11 |

| Registers . . . . .                       | 12 |

| Computer Timing . . . . .                 | 12 |

| System Diagram . . . . .                  | 13 |

| CONTROL SYSTEM . . . . .                  | 14 |

| MONROBOT XI COMMAND DESCRIPTION . . . . . | 15 |

| General . . . . .                         | 15 |

| Format . . . . .                          | 15 |

## ARITHMETIC INSTRUCTIONS

|                       |    |

|-----------------------|----|

| Add . . . . .         | 16 |

| Subtract . . . . .    | 17 |

| Detract . . . . .     | 18 |

| Multiply . . . . .    | 19 |

| Store . . . . .       | 21 |

| Load . . . . .        | 22 |

| Interchange . . . . . | 23 |

| Extract . . . . .     | 24 |

## CONTROL INSTRUCTIONS . . . . . 25

|                                |    |

|--------------------------------|----|

| Program Sequencing . . . . .   | 26 |

| Jump Unconditional . . . . .   | 28 |

| Jump Mark. . . . .             | 29 |

| Jump on Zero . . . . .         | 31 |

| Jump on High Order 1 . . . . . | 33 |

## INPUT-OUTPUT . . . . . 35

|                              |    |

|------------------------------|----|

| General. . . . .             | 35 |

| Input. . . . .               | 37 |

| FA 5 Output. . . . .         | 39 |

| Instruction Output . . . . . | 41 |

## SHIFT COMMANDS . . . . . 43

|                              |    |

|------------------------------|----|

| General. . . . .             | 43 |

| Decimal Shift Left . . . . . | 46 |

| Decimal Shift Right. . . . . | 48 |

| Binary Shift Left. . . . .   | 49 |

| Binary Shift Right . . . . . | 50 |

|                                                      |    |

|------------------------------------------------------|----|

| Binary Left End Around Shift . . . . .               | 51 |

| Binary Shift Right Maintain High Order Bit . . . . . | 52 |

| INTERVENTION INTERROGATE. . . . .                    | 53 |

| SPECIAL COMMANDS. . . . .                            | 56 |

| Clear FA 6 . . . . .                                 | 57 |

| Clear FA 5 . . . . .                                 | 58 |

| Set FA 6 to all Ones . . . . .                       | 59 |

| No Operation . . . . .                               | 60 |

| Stop . . . . .                                       | 61 |

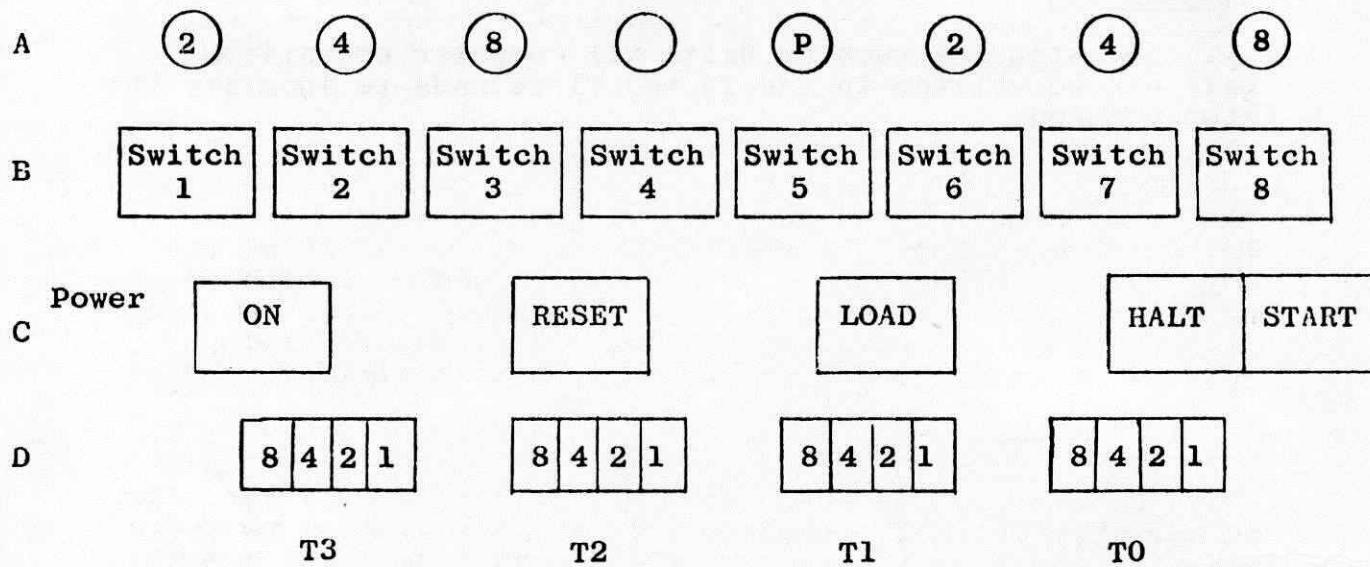

| CONTROL PANEL . . . . .                              | 62 |

| Control Switches . . . . .                           | 63 |

| Control Register Lights. . . . .                     | 64 |

| Input-Output Lights. . . . .                         | 64 |

| Intervention Interrogate Switches. . . . .           | 65 |

| Reset Entry. . . . .                                 | 66 |

| Starting Automatic Program . . . . .                 | 66 |

| Boot-Strap Techniques. . . . .                       | 67 |

| Boot-Strap . . . . .                                 | 68 |

| Computer Aid to Program Checking . . . . .           | 70 |

| OPERATION TIMING. . . . .                            | 72 |

| Minimum Access Coding. . . . .                       | 72 |

| One Drum Revolution Operations . . . . .             | 73 |

| Case I (one drum revolution) . . . . .               | 73 |

| Minimum Access for More Than One Drum Revolution . . | 74 |

| Case II (two drum revolutions) . . . . .             | 74 |

|                                                      |    |

|------------------------------------------------------|----|

| Case III (three drum revolutions) . . . . .          | 74 |

| INPUT-OUTPUT TIMING . . . . .                        | 75 |

| <b>APPENDIX I</b>                                    |    |

| Command and Access Time. . . . .                     | 76 |

| <b>APPENDIX II</b>                                   |    |

| Constant Generation. . . . .                         | 78 |

| <b>APPENDIX III</b>                                  |    |

| Table of Powers of 2 . . . . .                       | 82 |

| Typewriter Codes . . . . .                           | 83 |

| <b>APPENDIX IV</b>                                   |    |

| Binary to Decimal and Decimal to Binary Conversion . | 86 |

| <b>APPENDIX V</b>                                    |    |

| 2,048 Word Drum Address Structure . . . . .          | 88 |

## GENERAL

Monrobot Mark XI is a small, general purpose, digital, transistorized computer. Its number system is straight binary. The program is internally stored along with data on a magnetic drum. The computer addressing system is of the type known as one address. The magnetic drum contains 1,025 registers for computer word storage. Eight of these registers are called fast access registers. In addition to being fast access registers, some fast access registers have special computer functions. Each register in the computer storage system can hold a computer word of 32 binary bits. A computer word can be used to hold either data (numeric or alpha-numeric) or instructions. If a word is used for holding instructions, it will hold two computer instructions per word because each instruction is 16 binary bits. If a computer word is used to hold numeric data, the word can hold 30 binary bits of information (equivalent to nine decimal digits), a bit for use as an overflow test position, and a bit to indicate whether the data is positive or negative. Negative numbers are represented in the computer in two's complement. If a word is used for alpha-numeric storage, it can contain either five characters (each character equal to six binary bits) or six characters (each character equal to five binary bits). Figure 1 gives a representation of the computer words.

### Input

Input to the computer can be in any code. From one to three devices in any combination may be used in any Monrobot XI program. The input devices are typewriters, punched paper tape readers, punched card readers, teletype machines, and sixteen-key numeric keyboards.

### Output

Output from the computer can be in any code. From one to three devices in any combination may be used in a Monrobot XI program. The output devices are typewriters, paper tape punches, paper card punches, and teletype machines. The output devices may be operated by the program either independently or simultaneously in any combination.

### MONROBOT MARK XI COMPUTER WORDS

|                                                                                       |  |        |  |  |        |  |  |        |  |  |        |  |  |        |  |           |        |  |  |        |  |  |        |  |  |        |  |  |                    |            |  |                   |                   |

|---------------------------------------------------------------------------------------|--|--------|--|--|--------|--|--|--------|--|--|--------|--|--|--------|--|-----------|--------|--|--|--------|--|--|--------|--|--|--------|--|--|--------------------|------------|--|-------------------|-------------------|

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |        |  |  |        |  |  |        |  |  |        |  |  |        |  |           |        |  |  |        |  |  |        |  |  |        |  |  |                    | Power of 2 |  |                   |                   |

| A 16 bits                                                                             |  |        |  |  |        |  |  |        |  |  |        |  |  |        |  | B 16 bits |        |  |  |        |  |  |        |  |  |        |  |  |                    |            |  |                   | Instruc-tion Word |

| S O F<br>i v e<br>g e o<br>n r w                                                      |  |        |  |  |        |  |  |        |  |  |        |  |  |        |  | 30 bits   |        |  |  |        |  |  |        |  |  |        |  |  |                    |            |  |                   | Numeric Word      |

|                                                                                       |  | 6 bits |  |  |        |  |  | 6 bits |  |  |        |  |  | 6 bits |  |           |        |  |  | 6 bits |  |  |        |  |  | 6 bits |  |  |                    |            |  | Six-bit Character |                   |

|                                                                                       |  | 5 bits |  |  | 5 bits |  |  | 5 bits |  |  | 5 bits |  |  | 5 bits |  |           | 5 bits |  |  | 5 bits |  |  | 5 bits |  |  | 5 bits |  |  | Five-bit Character |            |  |                   |                   |

Figure 1

## SEXADECIMAL SYSTEM

Although the computer is completely binary and all data within the computer is binary, representation of computer words external to the computer is in the sexadecimal or base 16 system. There are two reasons for this representation. The first reason is that it is easier to recognize and write computer words in sexadecimal than in binary. The other reason is that nonautomatic input to the computer uses the sexadecimal system.

The sexadecimal system has 16 as its number base, just as the decimal system has 10, the octal system eight, and the binary system two. Table 1 gives the decimal, binary, octal, and sexadecimal equivalences.

| <u>Decimal</u> | <u>Binary</u> | <u>Octal</u> | <u>Sexadecimal</u> |

|----------------|---------------|--------------|--------------------|

| 0              | 0000          | 0            | 0                  |

| 1              | 0001          | 1            | 1                  |

| 2              | 0010          | 2            | 2                  |

| 3              | 0011          | 3            | 3                  |

| 4              | 0100          | 4            | 4                  |

| 5              | 0101          | 5            | 5                  |

| 6              | 0110          | 6            | 6                  |

| 7              | 0111          | 7            | 7                  |

| 8              | 1000          | 10           | 8                  |

| 9              | 1001          | 11           | 9                  |

| 10             | 1010          | 12           | S                  |

| 11             | 1011          | 13           | T                  |

| 12             | 1100          | 14           | U                  |

| 13             | 1101          | 15           | V                  |

| 14             | 1110          | 16           | W                  |

| 15             | <u>1111</u>   | 17           | X                  |

Table 1

Since there are 16 different characters in the sexadecimal system, the six characters over the decimal 10 have to be assigned names and symbols. The naming of the characters is arbitrary. In Monrobot Mark XI these characters were assigned the symbols and names of the English alphabetic letters S through X respectively.

As can be seen from Figure 2, each sexadecimal character represents four binary bits of information. This representation is called a tetrad of information. As each word in the computer holds 32 binary bits, then each word is comprised of eight tetrads.

### Tetrad Numbering

In referring to positions within a computer word, a combination of tetrad numbering and binary bit weight is used. Tetrads are numbered from 0 to 7; bits are numbered by their binary weight within the tetrad which can be 8, 4, 2, or 1. Figure 2 gives the tetrad and binary numbering for the computer word.

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |          |          |          |          |          |          |          |               | Powers of 2 |

|---------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|---------------|-------------|

| Tetrad 7                                                                              | Tetrad 6 | Tetrad 5 | Tetrad 4 | Tetrad 3 | Tetrad 2 | Tetrad 1 | Tetrad 0 | Tetrad Number |             |

| 8 4 2 1                                                                               | 8 4 2 1  | 8 4 2 1  | 8 4 2 1  | 8 4 2 1  | 8 4 2 1  | 8 4 2 1  | 8 4 2 1  | Binary Weight |             |

| +                                                                                     | +        | +        | +        | +        | +        | +        | +        |               |             |

Figure 2

In the manual, if a bit position or positions are referred to, they will be denoted by the tetrad number and weight. For example, the high order bit (2<sup>31</sup>) is referred to as T7-8.

### Conversion

This method of numbering the tetrads assigns to each tetrad position its positional exponent, to the base 16, in a sexadecimal number. Table 2 gives the equivalent values for each tetrad position.

| Tetrad | Base 16         | Base 2          | Decimal Equivalent |

|--------|-----------------|-----------------|--------------------|

| 0      | 16 <sup>0</sup> | 2 <sup>0</sup>  | 1                  |

| 1      | 16 <sup>1</sup> | 2 <sup>4</sup>  | 16                 |

| 2      | 16 <sup>2</sup> | 2 <sup>8</sup>  | 256                |

| 3      | 16 <sup>3</sup> | 2 <sup>12</sup> | 4096               |

| 4      | 16 <sup>4</sup> | 2 <sup>16</sup> | 65536              |

| 5      | 16 <sup>5</sup> | 2 <sup>20</sup> | 1048576            |

| 6      | 16 <sup>6</sup> | 2 <sup>24</sup> | 16777216           |

| 7      | 16 <sup>7</sup> | 2 <sup>28</sup> | 268435456          |

Table 2

Conversion from decimal to binary and binary to decimal external to the computer becomes a matter of finding the powers of 16 in a number and multiplying those powers by the binary weights of the power. Two examples below show how easily this is accomplished.

Example 1:

Convert the binary number

0000 0000 0000 0000 0010 1001 1101 1010

to decimal. This number is written in sexadecimal as 000029VS. Conversion involves selecting from the table the decimal equivalents of the powers, multiplying by the binary weight of that power, and summing the individual results.

| <u>Tetrad</u> | <u>Number</u> | <u>Decimal Equivalent</u> | <u>Binary Weight</u> | <u>Total</u> |

|---------------|---------------|---------------------------|----------------------|--------------|

| 7             | 0             | 0                         | 0                    |              |

| 6             | 0             | 0                         | 0                    |              |

| 5             | 0             | 0                         | 0                    |              |

| 4             | 0             | 0                         | 0                    |              |

| 3             | 2             | 4096                      | 2                    | 8192         |

| 2             | 9             | 256                       | 9                    | 2304         |

| 1             | V             | 16                        | 13                   | 208          |

| 0             | S             | 1                         | 10                   | <u>10</u>    |

|               |               |                           |                      | 10714        |

The result is 10714, the decimal equivalent of the number.

Example 2:

Convert the decimal number 10714 to binary. For conversion from decimal to binary, it is necessary to determine the binary weights of the powers of 16 that are in the decimal number. This is done by dividing the powers of 16 into the number. The quotient of each division gives the binary weights for that power's tetrad position. The remainder gives the value that is used by the next lowest power to obtain its binary weight. This process continues until the zero power or tetrad position is evaluated.

| <u>Power</u> | <u>Remainder</u> | <u>Quotient</u> | <u>Tetrad</u> |

|--------------|------------------|-----------------|---------------|

| 268435456    | 10714            | 0               | 7             |

| 16777216     | 10714            | 0               | 6             |

| 1048576      | 10714            | 0               | 5             |

| 65536        | 10714            | 0               | 4             |

| 4096         | 10714            | 2               | 3             |

| 256          | 2522             | 9               | 2             |

| 16           | 218              | 13              | 1             |

| 1            | 10               | 10              | 0             |

The result of the conversion is 000029VS when the sexadecimal equivalents are substituted for 13 and 10. Converting the sexadecimal number to binary is now a matter of substituting from Table 1.

These methods give reasonably easy and fast conversion between the number systems. If a Monroe automatic desk calculator is used, this process becomes extremely simple.

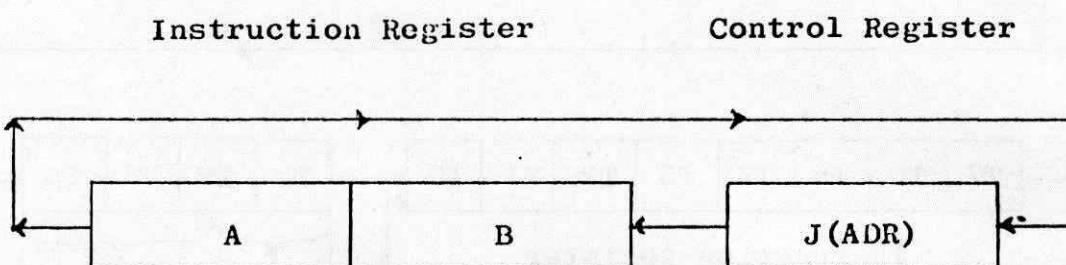

### Instructions

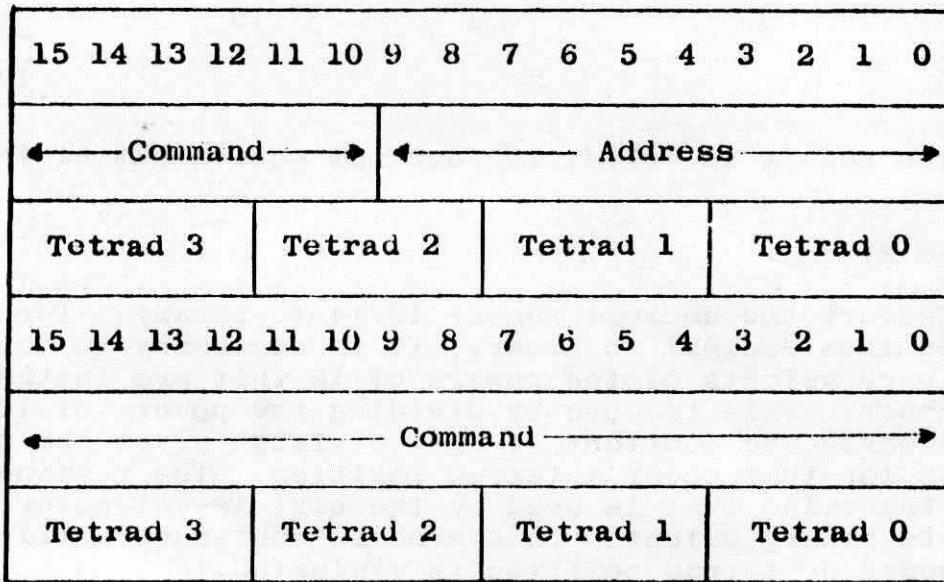

Instructions in the Monrobot Mark XI are 16 bits or four tetrads long. Therefore, one 32 bit register can hold two instructions. The 16 bits in an instruction word are divided into a command part of six bits and an address part of 10 bits. In the case of instructions that do not have an address, the entire 16 bits are referred to as a command. Figure 3 shows these two cases.

Figure 3

Instructions are written by the programmer not as binary bits but as tetrads. Writing in this manner does not cause any trouble except where the break between command bits and address bits occurs in tetrad 2. In this case sexadecimal values to three refer to the address portion; values above three have also a command portion.

The two instructions per register are referred to as the A step and the B step respectively. The machine always

executes the A step first and then the B step. It is never possible to branch to the B step. Figure 4 shows this instruction format.

|                                                                                       |  |          |  |          |  |          |  |          |  |          |  |          |  |          |        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--|----------|--|----------|--|----------|--|----------|--|----------|--|----------|--|----------|--------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |          |  |          |  |          |  |          |  |          |  |          |  |          |        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Command                                                                               |  | Address  |  |          |  |          |  |          |  | Command  |  | Address  |  |          |        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Tetrad 7                                                                              |  | Tetrad 6 |  | Tetrad 5 |  | Tetrad 4 |  | Tetrad 3 |  | Tetrad 2 |  | Tetrad 1 |  | Tetrad 0 |        |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Step A                                                                                |  |          |  |          |  |          |  |          |  |          |  |          |  |          | Step B |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

Figure 4

Table 3 gives the coding in sexadecimal and binary for the instructions that Monrobot Mark XI has in its repertory. The binary coding is for background information to the programmer only. When these instructions are explained in detail later in the manual, only the sexadecimal coding will be given. The commands are divided into two categories consisting of those commands which require storage addresses and those commands which refer to nonstorage operations, such as, input-output and shifting commands.

# MONROBOT MARK XI COMMANDS

|                                                                      | Binary                                     | Sexadecimal   |

|----------------------------------------------------------------------|--------------------------------------------|---------------|

| Detract                                                              | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0      | 3 2 1 0 Tetra |

| Multiply                                                             | 0 0 0 1 0 0   Address                      | 1 A D R       |

| Store                                                                | 0 1 0 1 0 0                                | 5 A D R       |

| Interchange                                                          | 1 0 1 1 0 0                                | T A D R       |

| Load                                                                 | 1 1 0 0 0 0                                | U A D R       |

| Subtract                                                             | 1 1 0 1 0 0                                | V A D R       |

| Add                                                                  | 1 1 1 0 0 0                                | W A D R       |

| Extract                                                              | 1 1 1 1 0 0   Address                      | X A D R       |

|                                                                      | 1 1 1 1 0 1                                | X A D R *     |

| Jump                                                                 | 0 0 1 1 0 0   Address                      | 3 A D R       |

| Jump Mark                                                            | 0 0 1 1 0 1                                | 3 A D R *     |

| Jump Zero                                                            | 0 1 1 0 0 0                                | 6 A D R       |

| Jump High 1                                                          | 0 1 1 1 0 0   Address                      | 7 A D R       |

| Input                                                                | 0 0 1 0   Address 0                        | 2 A 0 0       |

| Output                                                               | 1 0 1 0   Address 0                        | S B 7 X       |

| Instruction Output                                                   | 1 0 1 0   Address 1   Character            | S B+1 C C     |

| Multiply by 10                                                       | 1 0 0 0 0 0 0 0   Scale Factor             | 8 0 P N       |

| Divide by 10                                                         | 1 0 0 0 1 0 0 0                            | 8 8 P N       |

| Binary Shift Left                                                    | 1 0 0 1 0 0 0 0                            | 9 0 P N       |

| Binary Shift Right                                                   | 1 0 0 1 1 0 0 0                            | 9 8 P N       |

| Binary End Around                                                    | 1 0 0 0 1 1 0 0                            | 8 U P N       |

| Binary Shift Right Neg.                                              | 1 0 0 1 1 1 0 0   Scale Factor             | 9 U P N       |

| Intervention Interrogate                                             | 1 1 0 0 0 1 0 0   Address                  | U 4 A D       |

| Clear FA 6                                                           | 1 1 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0        | U 5 0 0       |

| Clear FA 5                                                           | 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0      | S 0 0 0       |

| Set FA 6                                                             | 1 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0      | U 4 0 0       |

| Stop                                                                 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0      | 0 0 0 0       |

| *These instructions add 400 to address to obtain sexadecimal coding. |                                            |               |

| ADR = 0 0 0 → 0 0 5                                                  |                                            |               |

| ADR                                                                  | = Address = 0 0 0 → 3 X X                  |               |

| A                                                                    | = Input Address = 2, 4, 8                  |               |

| B                                                                    | = Output Address = 0, 2, 4, 6, 8, S, U, W  |               |

| B + 1                                                                | = Instruction Output = 3, 5, 7, 9, T, V, X |               |

| CC                                                                   | = Any Eight-bit Character                  |               |

| PN                                                                   | = Shift from 1 → 8                         |               |

| AD                                                                   | = Intervention Interrogate Switch 1 → 8    |               |

Table 3

## NUMBER SYSTEM

The Monrobot Mark XI is a fixed point binary integer computer. The binary point is located to the right of the number ( $2^0$  position). All numbers used in the computer are treated as integers. Numbers less than one must be scaled so that they are greater than one. Special shift commands are provided to aid in scaling. These shift commands also assist in the decimal-to-binary and binary-to-decimal conversions which must be programmed. Appendix 4 gives methods for conversion using the Monrobot XI shift commands.

The maximum size of a number in the computer is 32 bits, which is equivalent to the decimal number  $2^{32} - 1$  (4294967295). The practical size of a number is 30 bits, which is equivalent to the decimal number  $2^{30} - 1$  (1073741823). The latter is the number size which will be used when arithmetic operations are discussed in this manual. Negative numbers within the computer are maintained in two's complement form. The high order bit (T7-8) of every numeric register is treated as the sign position. If this bit is zero, the number is regarded as positive. If this bit is one, the number is regarded as negative. In the arithmetic operations of addition, subtraction, and multiplication, the results will be signed correctly if the operands do not exceed 30 bits of information.

### Overflow

Numbers which exceed 32 bits as a result of an operation are said to overflow. The computer gives no automatic indication of this overflow. The programmer must test for overflow through the program and prevent numbers from becoming large enough to exceed capacity. When 30 bits are used as the number size, the T7-4 bit position (next to high order) is used as the overflow test position. This position must always have the same value after an arithmetic operation as the sign position (T7-8) or the result exceeds 30 bits in absolute value. In effect, if the result is positive, T7-4 must be zero; if the result is negative, T7-4 must be one. Testing whether overflow has occurred is a function of the programmer through the program. Overflow exceeding 30 bits cannot be permitted because subsequent overflows will change the value of the sign bit from zero to one and one to zero and exceed the capacity of 32 bits. Figure 1 gives a representation of the number word in Monrobot XI.

## STORAGE SYSTEM

The Monrobot Mark XI storage system is a magnetic drum. The drum rotates 5,124 times per minute making a drum revolution equivalent to 11.7 milliseconds. The magnetic drum has located on it 1,025, 32-bit registers. Of these registers, 1,017 are in what is called general storage and are available once each drum revolution. The other eight registers are in what is called fast access storage and are available 16 times per drum revolution.

### General Storage

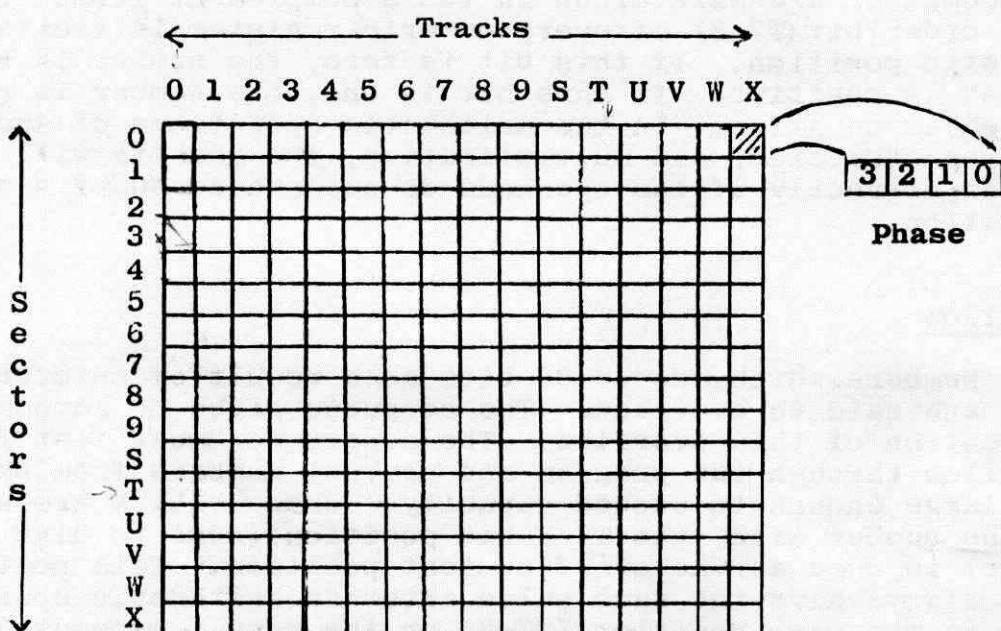

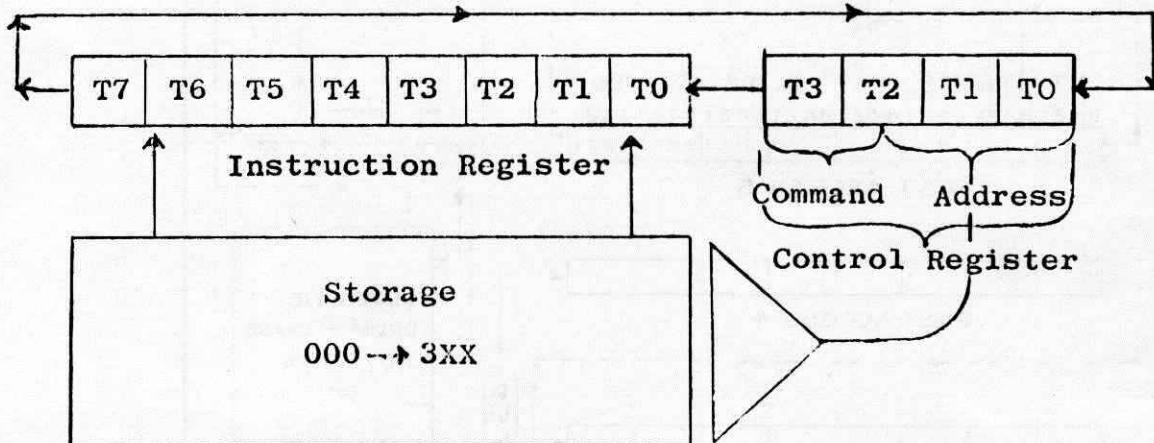

The 1,017 general storage registers are divided into 16 tracks along the axis of the drum. Each track is divided into 16 parts called sectors; within each sector are four registers called phases. Figure 5 shows the general storage drum system.

Figure 5

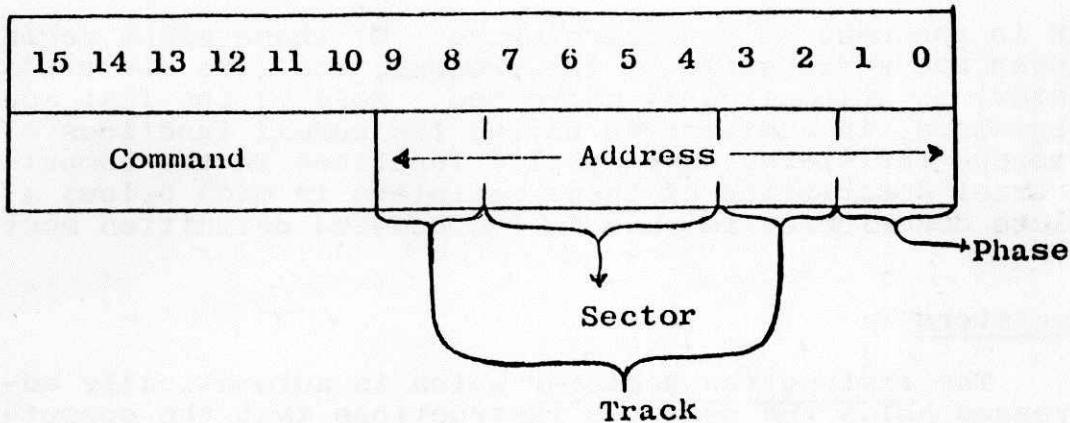

Addressing a general storage register requires 10 bits. Four bits denote the track, four bits indicate the sector on the track, and two bits indicate the phase within the sector. Figure 6 shows how the address bits are divided within an instruction word.

Figure 6

Since all registers are addressed in sexadecimal coding, the programmer does not concern himself with the binary coding of the address. For general information, an example of sexadecimal address coding and its breakdown into the binary address coding is given below.

General storage register 767 in decimal is 2XX in sexadecimal; 2XX = 1011111111 in binary. This register is located in track T (1011) sector X (1111) and phase 3 (11).

#### Access Time

Every general storage track has a device called a read-write head for obtaining data from a register and recording data into a register. Each sector around the track is presented to this read-write head once every drum revolution. When an instruction calls for a general storage address, the computer cannot read from the register or write into the register until the sector in which that register is located is under the read-write head. The time it takes from when the instruction is given to the time when the sector is available is called access time. Access time can range from zero sector times (sector is under read-write head) to 15 sector times (sector is a complete drum revolution away). Average access time to general storage registers is eight word times.

#### Fast Access Storage

The magnetic drum has two tracks which hold four registers each. These registers are called fast access registers because they are available every sector time (16 times a drum revolution) rather than once a drum revolution.

as in the case of general storage. Of these eight registers, seven are addressable by the program, one (the instruction register) is automatically addressed. Some of the fast access registers, in addition to having the normal functions of storage registers, have special functions in the computer. A brief description of these registers is made below; a complete description is made in the command definition sections.

### Registers

The Instruction Register which is automatically addressed holds the next two instructions that the computer may execute.

Fast Access 6 (address 0 0 6) performs the function of the accumulator. It holds one of the operands and most of the results in arithmetic operations. It receives the input character in input operations, holds the high order portion of the product in multiplication, and the remainder in de-traction.

Fast Access 5 (address 0 0 5) holds the low order portion of the product in multiplication, the number of detractions in the detract operation, the output character in the output operation, and is part of the end around shift.

Fast Access 4 (address 0 0 4) holds the multiplicand in the multiply operation and the detractor in the detract operation.

Fast Access 2 (address 0 0 2) receives the contents of the instruction register in the jump mark instruction.

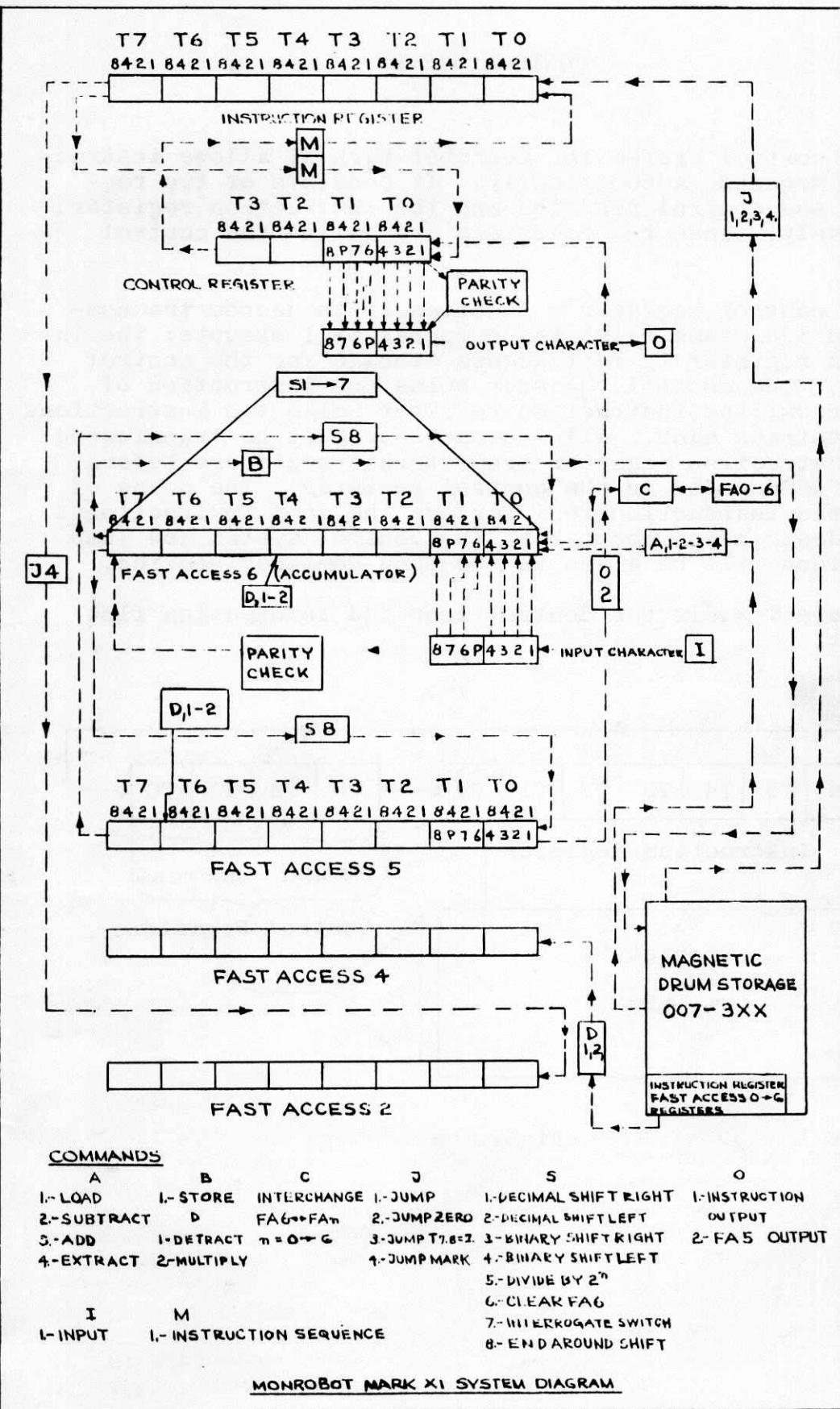

Fast Access Registers 3 (address 0 0 3), 1 (address 0 0 1), 0 (address 0 0 0) have no special functions and can always be used as storage registers. Figure 7, which is the system diagram of Monrobot Mark XI, shows the flow of information between these registers and the rest of the computer.

### Computer Timing

All timing in the computer is based on the drum revolution speed and the number of sectors in a revolution. Since there are 16 sectors and a drum speed of 11.7 milliseconds, a sector time is equivalent to .73 milliseconds. All computer operations are measured in sector times. The minimum instruction time is four sector times. The actual length of time depends upon two factors: execution time and access time. Execution time is the time necessary to execute the command; access time is the time necessary to obtain the contents of the addressed register. Appendix I gives data on execution times for each command and page 72 gives rules for minimizing access time.

FIGURE 7

## CONTROL SYSTEM

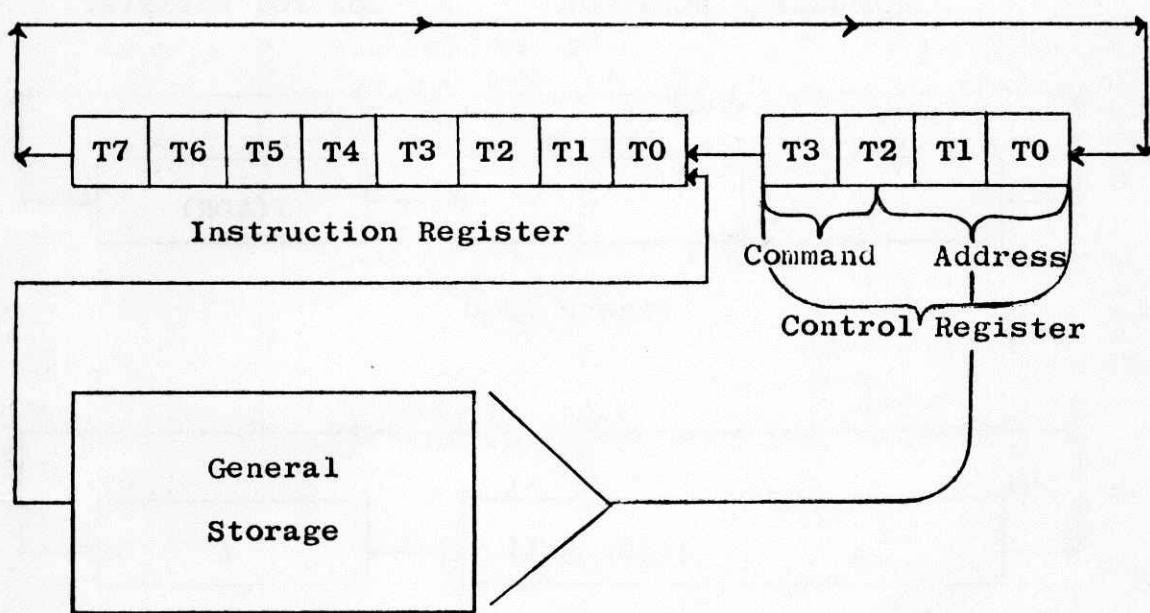

The control system for Monrobot Mark XI allows instructions to sequence automatically. It consists of two registers: the control register and the instruction register. Collectively, these two registers are called the control loop.

The control register's function is to decode the commands and addresses which the computer will execute; the instruction register is fast access storage for the control register. The control register holds one instruction of four tetrads; the instruction register holds two instructions of four tetrads each. All instructions must be transferred to the instruction register from storage registers before they can be decoded in the control register. The means of loading the instruction register are the jump instructions. Further description about both the control system and jump instructions will be given in the jump commands section.

Figure 8 shows the control loop and information flow within it.

Figure 8

## MONROBOT XI COMMAND DESCRIPTION

### General

For this manual Monrobot XI commands have been divided into two groups, namely, commands that require a storage address and commands that do not require a storage address. Each of these two groups has again been subdivided. Addressable commands are either arithmetic or control commands. Nonaddressable commands are either shifting commands or input-output commands. Arithmetic commands will be described first, then control, input-output, and shifting commands.

### Format

Each command will be described in sexadecimal notation. The following format will be used.

|                             |                                                                                                                                                                                                    |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Command</u>              | English words for command.                                                                                                                                                                         |

| <u>Code</u>                 | Sexadecimal coding of command.                                                                                                                                                                     |

| <u>Instruction</u>          | Sexadecimal code of command and variations to command. Variations are mnemonic with range of variations written on the right.                                                                      |

| <u>Fast Access Register</u> | This will give the fast access registers which the command uses or may affect by changing the values of these registers after the operation.                                                       |

| <u>Description</u>          | English language description of command. The term FA used in the description refers to fast access.                                                                                                |

| <u>Example</u>              | This gives a coded example of the command with values in the affected registers both prior to the operation and subsequent to the operation. These values are in decimal and sexadecimal notation. |

Command

Add

Code

X - - -

Instruction

X A D R

A D R = 0 0 0 → 3 X X

Fast Access Register

0 0 6

Description

The add command adds the contents of the addressed storage register to the contents of FA 6 (accumulator) and places the sum in FA 6 (accumulator). The addressed storage register is unchanged by this command. Negative and positive numbers can be added, and the correct algebraic result will occur. Carries exceeding 30 bits will affect the overflow test position (T7-4), carries exceeding the overflow test position will affect the sign position (T7-8), and carries beyond this position are lost.

Example

Instruction

X 0 0 3

Register

Decimal

Sexadecimal

Before Add

0 0 3

4096

1000

0 0 6

256

100

After Add

0 0 3

4096

1000

0 0 6

4352

1100

Instruction

X 0 0 6

Before Add

0 0 6

999999999

3T9SU9XX

After Add

0 0 6

1999999998

773593XW

This example shows how overflow affects the overflow test position.

## ARITHMETIC INSTRUCTIONS

Command                    **Subtract**

Code                    **W - - -**

Instruction            **W A D R**                    **A D R = 0 0 0 → 3 X X**

Fast Access Register

**0 0 6**

Description

The subtract command subtracts the contents of the addressed storage register from the contents of FA 6 (accumulator) and places the remainder in FA 6 (accumulator). The addressed register is unchanged by this command.

Both negative and positive numbers can be subtracted, and the correct algebraic result will occur. Negative remainders will be expressed in two's complement. Borrows exceeding 30 bits will affect the overflow test position (T7-4), borrows exceeding the overflow test position will affect the sign position (T7-8), and borrows beyond the sign position are lost.

Example

| <u>Instruction</u>     | <b>W 1 3 U</b>     | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

|------------------------|--------------------|-----------------|----------------|--------------------|

| <b>Before Subtract</b> |                    | <b>1 3 U</b>    | <b>25</b>      | <b>19</b>          |

|                        |                    | <b>0 0 6</b>    | <b>52</b>      | <b>34</b>          |

| <b>After Subtract</b>  |                    | <b>1 3 U</b>    | <b>25</b>      | <b>19</b>          |

|                        |                    | <b>0 0 6</b>    | <b>27</b>      | <b>1T</b>          |

| <br><u>Instruction</u> | <br><b>W 2 X X</b> |                 |                |                    |

| <b>Before Subtract</b> |                    | <b>2 X X</b>    | <b>346</b>     | <b>15S</b>         |

|                        |                    | <b>0 0 6</b>    | <b>345</b>     | <b>159</b>         |

| <b>After Subtract</b>  |                    | <b>2 X X</b>    | <b>346</b>     | <b>15S</b>         |

|                        |                    | <b>0 0 6</b>    | <b>- 1</b>     | <b>XXXXXXXX</b>    |

|                    |                |

|--------------------|----------------|

| <u>Command</u>     | <b>Detract</b> |

| <u>Code</u>        | 1 - - -        |

| <u>Instruction</u> | 1 A D R        |

A D R = 0 0 0 → 3 X X

Fast Access Registers

004, 005, 006

Description

The detract command transfers the contents of the addressed register automatically to FA 4. It then subtracts the contents of FA 4 from the contents of FA 6 (accumulator) until FA 6 is less than the contents of FA 4. For every such subtraction that is made, a one is added to the low order (T0-1) position of FA 5. The contents of both FA 6 and FA 4 are considered as positive numbers. If the contents of the addressed register are zero when this command is used, the detract operation will not cease unless the computer is reset. The contents of the addressed storage register are unchanged by this command.

Examples

Instruction      1 0 6 3

|                       | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

|-----------------------|-----------------|----------------|--------------------|

| <b>Before Detract</b> | 0 6 3           | 5              | 5                  |

|                       | 0 0 6           | 321            | 141                |

|                       | 0 0 5           | 0              | 0                  |

|                       | 0 0 4           | 652            | 28U                |

| <b>After Detract</b>  | 0 6 3           | 5              | 5                  |

|                       | 0 0 6           | 1              | 1                  |

|                       | 0 0 5           | 64             | 40                 |

|                       | 0 0 4           | 5              | 5                  |

Command      **Multiply**

Code      **5 - - -**

Instruction      **5 A D R**      **A D R = 0 0 0 → 3 X X**

Fast Access Registers

**004, 005, 006**

Description

The multiply command transfers the contents of the addressed register automatically to FA 4. It then multiplies the contents of FA 4 by the contents of FA 6 (accumulator) to develop a 64-bit product. The low order 32 bits of this product are in FA 5, and the high order 32 bits are in FA 6. If the product is negative, it will be represented in two's complement in both FA 5 and FA 6. The contents of the addressed register are not affected by this command.

Examples

Instruction      **5 2 3 X**

|                        | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

|------------------------|-----------------|----------------|--------------------|

| <b>Before Multiply</b> | <b>2 3 X</b>    | <b>350</b>     | <b>15W</b>         |

|                        | <b>0 0 6</b>    | <b>15</b>      | <b>X</b>           |

|                        | <b>0 0 5</b>    | <b>6721</b>    | <b>1841</b>        |

|                        | <b>0 0 4</b>    | <b>621</b>     | <b>26V</b>         |

| <b>After Multiply</b>  | <b>2 3 X</b>    | <b>350</b>     | <b>15W</b>         |

|                        | <b>0 0 6</b>    | <b>0</b>       | <b>0</b>           |

|                        | <b>0 0 5</b>    | <b>5250</b>    | <b>1482</b>        |

|                        | <b>0 0 4</b>    | <b>350</b>     | <b>15W</b>         |

Instruction      **5 0 0 6**

|                        |              |              |               |

|------------------------|--------------|--------------|---------------|

| <b>Before Multiply</b> | <b>0 0 6</b> | <b>65536</b> | <b>100000</b> |

|                        | <b>0 0 5</b> | <b>216</b>   | <b>V8</b>     |

|                        | <b>0 0 4</b> | <b>1248</b>  | <b>4W0</b>    |

|                        | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

|------------------------|-----------------|----------------|--------------------|

| <b>After Multiply</b>  | 0 0 6           | 1              | 1                  |

|                        | 0 0 5           | 0              | 0                  |

|                        | 0 0 4           | 65536          | 10000              |

| <b>Instruction</b>     | 5 3 W W         |                |                    |

| <b>Before Multiply</b> | 3 W W           | 999999999      | 3T9SU9XX           |

|                        | 0 0 6           | 999999999      | 3T9SU9XX           |

|                        | 0 0 5           | 0              | 0                  |

|                        | 0 0 4           | 10             | S                  |

| <b>After Multiply</b>  | 3 W W           | 999999999      | 3T9SU9XX           |

|                        | 0 0 6           | 232830643      | VWOT6T3            |

|                        | 0 0 5           | 808348673      | 302W6U01           |

|                        | 0 0 4           | 999999999      | 3T9SU9XX           |

Command

Store

Code

T - - -

Instruction

T A D R

A D R = 0 0 0 → 3 X X

Fast Access Registers

0 0 6

Description

The store command replaces the contents of the addressed storage register with the contents of FA 6 (accumulator). FA 6 is unchanged by the store command. The store command is the only command that will change the contents of register 0 0 7 → 3 X X.

If the address of the store instruction is 0 0 6, the contents of FA 6 will replace the contents of FA 4, but the contents of FA 6 will remain unchanged.

ExampleInstruction

T 3 2 3

|                     | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

|---------------------|-----------------|----------------|--------------------|

| <b>Before Store</b> | 3 2 3           | 625            | 271                |

|                     | 0 0 6           | 15630          | 3V0W               |

| <b>After Store</b>  | 3 2 3           | 15630          | 3V0W               |

|                     | 0 0 6           | 15630          | 3V0W               |

Command

Load

Code

V - - -

Instruction

V A D R

A D R = 0 0 0 → 3 X X

Fast Access Register

0 0 6

Description

The load command replaces the contents of FA 6 (accumulator) with the contents of the addressed storage register. The addressed storage register is unchanged by this command.

ExampleInstruction

V 0 6 0

|             | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

|-------------|-----------------|----------------|--------------------|

| Before Load | 0 6 0           | 345189         | 54465              |

|             | 0 0 6           | 0              | 0                  |

| After Load  | 0 6 0           | 345189         | 54465              |

|             | 0 0 6           | 345189         | 54465              |

Command**Interchange**Code**U - - -**Instruction**U A D R****A D R = 0 0 0 → 0 0 6**Fast Access Registers**0 0 6 and addressed FA register**Description

The interchange command replaces the contents of the addressed fast access register with the contents of FA 6 (accumulator) and places the contents of the addressed fast access register into FA 6 (accumulator).

If the address of this command is 0 0 6, the contents of FA 6 will replace the contents of FA 4. However, the contents of FA 6 will remain unchanged.

Example**Instruction****U 0 0 1**

|                           | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

|---------------------------|-----------------|----------------|--------------------|

| <b>Before Interchange</b> | 0 0 6           | 25002          | 61SS               |

|                           | 0 0 1           | 20             | 14                 |

| <b>After Interchange</b>  | 0 0 6           | 20             | 14                 |

|                           | 0 0 1           | 25002          | 61SS               |

|                    |                |

|--------------------|----------------|

| <u>Command</u>     | <u>Extract</u> |

| <u>Code</u>        | X 4 - -        |

| <u>Instruction</u> | X (4+A) D R    |

A D R = 0 0 0 → 3 X X

Fast Access Register

0 0 6

Description

The extract command compares the 32 bit positions in the addressed storage register with the 32 bit positions in FA 6 (accumulator). Wherever a one occurs in corresponding bit positions, a one is placed in that bit position in FA 6; wherever a one is not present in both positions, a zero is placed in that bit position. The addressed storage register is not changed by this command.

This command is a logical multiplication command.

Example

|                       |         |                 |                |                    |

|-----------------------|---------|-----------------|----------------|--------------------|

| <u>Instruction</u>    | X 5 6 3 | <u>Register</u> | <u>Decimal</u> | <u>Sexadecimal</u> |

| <u>Before Extract</u> | 1 6 3   |                 | Not            | 11V7               |

|                       | 0 0 6   |                 | Applicable     | X9                 |

| <u>After Extract</u>  | 1 6 3   |                 |                | 11V7               |

|                       | 0 0 6   |                 |                | V1                 |

| <u>Instruction</u>    | X 4 0 2 |                 |                |                    |

| <u>Before Extract</u> | 0 0 2   |                 |                | XXXX0000           |

|                       | 0 0 6   |                 |                | 20093200           |

| <u>After Extract</u>  | 0 0 2   |                 |                | XXXX0000           |

|                       | 0 0 6   |                 |                | 20090000           |

## CONTROL INSTRUCTIONS

Monrobot Mark XI has four control or jump instructions which permit conditional and unconditional branching of program control. Prior to describing the four jump instructions, a further description of the control loop will be made to facilitate an understanding of instruction sequencing in the computer. Figure 9 shows the control loop which consists of the control register and instruction register.

Figure 9, Control Loop

The function of the control register is to decode instructions; the function of the instruction register is to provide fast access storage for the control register. The instruction register holds the instructions that will be executed or have been executed. All instructions must be transferred to the instruction register from storage before they can be executed by the control register. The jump commands are the commands that do this transfer.

As can be seen from Figure 9, three instructions are present in the control loop. Two of these instructions are in the instruction register; one (currently being executed) is in the control register. Of these three instructions one must always be a jump instruction in order to load the instruction register with the next two instructions in the program sequence.

## Program Sequencing

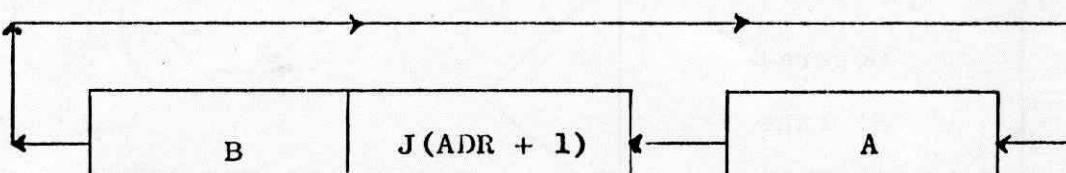

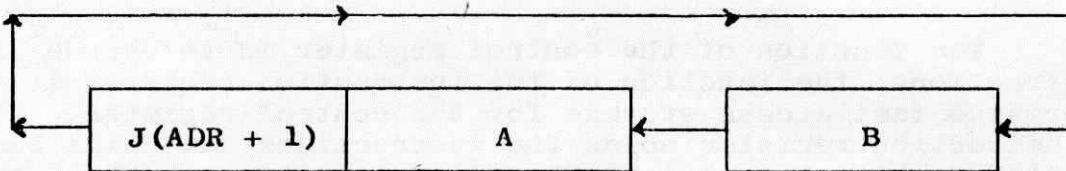

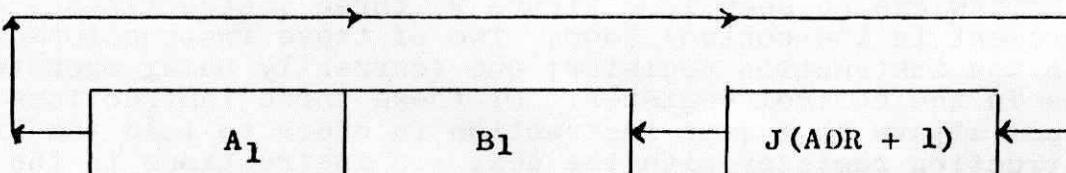

Program sequencing operates by the jump instruction bringing the contents of the desired register into the instruction register, executing the two instructions in the control register, and then automatically bringing the next register in sequence into the instruction register unless one of the instructions executed was a jump instruction. This jump instruction would have loaded the contents of the instruction register with two instructions and started a new automatic sequence.

Figure 10.0

Figure 10.1

Figure 10.2

Figure 10.3

The Figures 10.0 through 10.3 show how Monrobot Mark XI program sequencing operates. Figure 10.0 shows a jump instruction in the control register. This jump instruction has loaded the instruction register with the contents of the storage register addressed by the jump command. The computer then automatically shifts the A step from the instruction register into the control register. The B step moves up to replace the A step. The jump instruction has a one automatically added to its address portion and is moved into the positions vacated by the B step. Figure 10.1 shows this operation. After the A step has been executed, the B step is shifted into the control register. The augmented jump command moves into the vacated B step positions, and the executed A step into the jump position. Figure 10.2 shows this operation. Once the B step has been executed, the entire process is repeated with the control register being loaded with the jump command with its address increased by one. Figure 10.3 gives this operation. In this manner automatic sequencing will continue unless either the A step or the B step contains a jump instruction. This jump command will load the instruction register as in Figure 10.0 and then have its address augmented automatically to start a new automatic sequence.

Although three instructions are constantly circulating in the control loop, the only time a jump instruction is written by the programmer is when the control sequence is to be changed from being automatically sequenced by the computer.

On the execution of instructions from the instruction register, the A step is always done first and then the B step. It is never possible to alter this sequence. Figures 10.0 to 10.3 show this sequencing.

The jump command which does the automatic sequencing is the unconditional jump. Any other jump commands which may load the instruction register become unconditional jumps in the control loop after they have loaded the instruction register.

|                    |                    |

|--------------------|--------------------|

| <u>Command</u>     | Jump Unconditional |

| <u>Code</u>        | 3 - - -            |

| <u>Instruction</u> | 3 A D R            |

$$A D R = 0 0 0 \rightarrow 3 X X$$

### Fast Access Registers

#### Instruction

#### Description

The jump unconditional command replaces the contents of the instruction register with the contents of the addressed register. The previous sequence of instructions is interrupted, and a new sequence starting with the A step of the addressed register is started. The contents of the addressed register are unchanged by this command.

#### Example

| Instruction | 3 2 0 0 | Register    | Sexadecimal |

|-------------|---------|-------------|-------------|

| Before Jump | 2 0 0   |             | V002T315    |

|             |         | Instruction | X001W216    |

| After Jump  | 2 0 0   |             | V002T315    |

|             |         | Instruction | V002T315    |

Command      Jump Mark

Code      3 4 - -

Instruction      3 (4+A) D R      A D R = 0 0 0 → 3 X X

Fast Access Registers

Instruction, 0 0 2

Description

The jump mark command replaces the contents of FA 2 with the contents of the instruction register and then replaces the contents of the instruction register with the contents of the addressed register. The previous sequence of instructions is interrupted and a new sequence beginning with the A step of the addressed register is started. The contents of the addressed register are unchanged by this command.

Examples

|                  |                 |                    |

|------------------|-----------------|--------------------|

| Instruction      | 3 6 1 2         |                    |

|                  | <u>Register</u> | <u>Sexadecimal</u> |

| Before Jump Mark | 2 1 2           | X00530XX           |

|                  | Instruction     | 320XX001           |

|                  | 0 0 2           | 00000036           |

| After Jump Mark  | 2 1 2           | X00530XX           |

|                  | Instruction     | X00530XX           |

|                  | 0 0 2           | 320XX001           |

| Instruction      | 3 5 X X         |                    |

| Before Jump Mark | 1 X X           | V301T001           |

|                  | Instruction     | W09X3213           |

|                  | 0 0 2           | 00000000           |

| After Jump Mark  | 1 X X           | V301T001           |

|                  | Instruction     | V301T001           |

|                  | 0 0 2           | W09X3213           |

The jump mark command permits program branching with memory of the program register which caused the program branch. FA 2 contains this memory. The memory consists of the contents of the instruction register when the jump mark command was being executed in the control register. One of the instructions in FA 2 after the jump mark command is the executed A step if the jump mark was the B step or the unexecuted B step if the jump mark command was the A step of the program register which contained the jump mark command. The other instruction is the automatic jump instruction which is always present in the control loop. The address of this automatic jump instruction is one more than the program register which contained the jump mark. This automatic jump instruction would have continued program sequencing if the jump mark instruction had not been written as either the A or B step. Since this jump is transferred to FA 2 by the jump mark command, any subsequent jump to FA 2 will retransfer program control to the program register after the program register which contained the jump mark command. If the jump mark command was the A step of the program register, the unexecuted B step would be the first instruction performed when control was returned to FA 2. The automatic jump which actually returns the program to the desired sequence would be executed after this step. If the jump mark was in the B step only the automatic jump is executed when control is returned to FA 2.

It is not necessary to keep the marked instruction in FA 2. The marked instruction can be transferred to any storage register, allowing FA 2 to be used for working storage or receiving more mark instructions. To return to the previous sequence, the program would jump to the register where the contents of FA 2 had been transferred.

The jump mark instruction makes possible effective use of subroutines in Monrobot Mark XI. Entrance to the subroutines is made through the jump mark instruction. Exit from the subroutines is a jump to the register where the mark has been placed. The program then resumes its sequence at the instruction step after the jump mark instruction.

|                    |              |

|--------------------|--------------|

| <u>Command</u>     | Jump on Zero |

| <u>Code</u>        | 6 - - -      |

| <u>Instruction</u> | 6 A D R      |

A D R = 0 0 0 → 3 X X

### Fast Access Registers

#### Instruction

#### Description

The jump on zero command replaces the contents of the instruction register with the contents of the addressed storage register if the contents of FA 6 (accumulator) are equal to zero. The previous sequence of instructions is interrupted and a new sequence starting with the A step of the addressed register is begun.

If the contents of FA 6 (accumulator) are not equal to zero, the program continues by executing the next instruction from the instruction register.

This command, whether successful or unsuccessful, does not change the contents of the addressed storage register.

#### Examples

| Instruction         | 6 3 2 5     | Register | Sexadecimal |

|---------------------|-------------|----------|-------------|

| Before Jump on Zero | 3 2 5       |          | T0013096    |

|                     | Instruction |          | 3300X002    |

|                     | 0 0 6       |          | 0           |

| After Jump on Zero  | 3 2 5       |          | T0013096    |

|                     | Instruction |          | T0013096    |

|                     | 0 0 6       |          | 0           |

| <b>Instruction</b>         | <b>6 1 X X</b>     |                    |

|----------------------------|--------------------|--------------------|

|                            | <u>Register</u>    | <u>Sexadecimal</u> |

| <b>Before Jump on Zero</b> | <b>1 X X</b>       | <b>V2TTX001</b>    |

|                            | <b>Instruction</b> | <b>3205X005</b>    |

|                            | <b>0 0 6</b>       | <b>12</b>          |

| <b>After Jump on Zero</b>  | <b>1 X X</b>       | <b>V2TTX001</b>    |

|                            | <b>Instruction</b> | <b>3205X005</b>    |

|                            | <b>0 0 6</b>       | <b>12</b>          |

*Negative.*

|                    |                      |

|--------------------|----------------------|

| <u>Command</u>     | Jump on High Order 1 |

| <u>Code</u>        | 7 - - -              |

| <u>Instruction</u> | 7 A D R              |

A D R = 0 0 0 → 3 X X

Fast Access Registers

Instruction

Description

The jump on high order 1 command replaces the contents of the instruction register with the contents of the addressed storage register if and only if the high order bit (T7-8) of FA 6 (accumulator) is equal to one. The previous sequence of instructions is interrupted, and a new sequence is begun starting with the A step of the addressed register. If the high order bit (T7-8) of FA 6 (accumulator) is equal to zero, the program continues by executing the next instruction from the instruction register.

This command, whether successful or unsuccessful, does not change the contents of the addressed storage register.

Example

Instruction

7 0 6 0

Register

Sexadecimal

|                    |       |          |

|--------------------|-------|----------|

| Before Jump High 1 | 0 6 0 | U005X004 |

|--------------------|-------|----------|

Instruction

3261T050

0 0 6

80000000

|                   |       |          |

|-------------------|-------|----------|

| After Jump High 1 | 0 6 0 | U005X004 |

|-------------------|-------|----------|

Instruction

U005X004

0 0 6

80000000

|             |         |

|-------------|---------|

| Instruction | 7 3 0 0 |

|-------------|---------|

|                    |       |          |

|--------------------|-------|----------|

| Before Jump High 1 | 3 0 0 | X012T005 |

|--------------------|-------|----------|

Instruction

X0013310

0 0 6

00005602

|                   | <u>Register</u> | <u>Sexadecimal</u> |

|-------------------|-----------------|--------------------|

| After Jump High 1 | 3 0 0           | X012T005           |

|                   | Instruction     | X0013310           |

|                   | 0 0 6           | 00005602           |

In most cases this command can be thought of as a jump on negative since all negative numbers must have a high order bit. However, shift commands and the input command also affect the high order bit position of FA 6 so that the jump on high 1 is more general.

## INPUT-OUTPUT

### General

The Monrobot Mark XI input-output unit is the character. Every time an input or output command is given, one character which may be up to two tetrads (eight bits) is either read into the computer from an input device or written on the output devices. The programmer is responsible through the program for the conversion, transfer, and manipulation of all characters so that they form computer words on input, and for the inverse, that computer words form characters on output. Special shift commands (described in section "Shift Commands," page 47) are provided to aid the programmer in performing this program function. Appendix 4 gives some conversion and manipulation methods.

The Monrobot Mark XI system can have from one to three input and output devices in operation in the same program. Only one input device can read a character into the computer during an input command; however, characters may be sent to one, two, or three devices simultaneously during an output command.

All characters read into or out of the computer have parity bits. Parity is defined as odd parity. That is, the sum of the one bits in each character must equal an odd number. All characters read out of the computer have odd parity assigned to them. Input characters that do not have odd parity are singled out to the program.

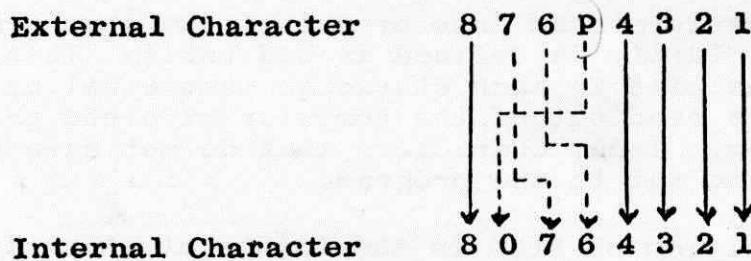

The position of bits in the input-out character is represented differently when the character is within the Monrobot Mark XI than when the character is external to the device. Characters external to the Monrobot Mark XI have the following form, where Lines A and C give the binary weight of the bit position. Line B gives the numeric order of the bits reading from right to left where P represents the location of the parity bit.

|   |         |         |                      |

|---|---------|---------|----------------------|

| A | 8 4 2 1 | 8 4 2 1 | Binary Weight        |

| B | 8 7 6 P | 4 3 2 1 | Numeric Bit Position |

| C | T1      | T0      | Tetrad Position      |

Characters internal to the Monrobot Mark XI have the following form where Lines A and C give the binary weight of

|   |         |         |

|---|---------|---------|

| A | 8 4 2 1 | 8 4 2 1 |

| B | 8 P 7 6 | 4 3 2 1 |

| C | T1      | T0      |

the bit position. Line B gives the position of the character bits of the external character when automatically rearranged by the computer for its internal use. The P position is shifted to the T1-4 position and is automatically set to zero. The T1-4 and T1-2 positions of the external character are shifted to the T1-2 and T1-1 positions respectively. The other positions remain exactly the same. Figure 11 shows this rearrangement.

Figure 11

This rearrangement allows most characters to enter the computer as six bit characters and allows for maximum density of packing characters into a computer register.

| <u>Command</u>     | <u>Input</u> |              |

|--------------------|--------------|--------------|

| <u>Code</u>        | 2 2 0 0      | Device 1     |

|                    | 2 4 0 0      | Device 2     |

|                    | 2 8 0 0      | Device 3     |

| <u>Instruction</u> | 2 A 0 0      | A = 2, 4, 8. |

## Fast Access Registers

006

### Description

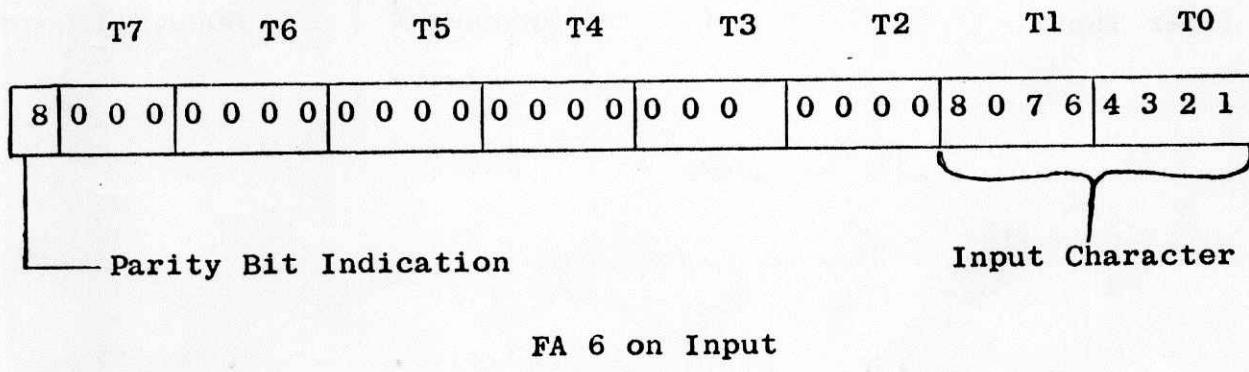

The input command replaces the contents of FA 6 (accumulator) with the character that is at the input device specified by the instruction. The character which may be up to eight bits (two tetrads) is placed in the low order (T0 and T1) positions of FA 6. All other bit positions are set to zero automatically with the exception of the high order bit position (T7-8). This position is set to one if the input character has even parity; it is set to zero if the input character has odd parity. Figure 12 shows FA 6 for this command.

### FA 6 on Input

Figure 12

The character read into the T0-T1 tetrads has its bit positions rearranged as indicated from its input format of 876P4321. When an input command addresses a device, the addressed device must have a character available or the computer will wait at that input device until a character is made available. No other computer operations can proceed until the input command has been executed.

Example

Input from Device 3

| Instruction  | 2 8 0 0         |                    |                                        |

|--------------|-----------------|--------------------|----------------------------------------|

|              | <u>Register</u> | <u>Sexadecimal</u> | <u>Binary Character Representation</u> |

| Before Input | 0 0 6           | XXX00000           | 01100001                               |

| After Input  | 0 0 6           | 00000031           | 00110001                               |

Input from Device 2, Parity Error

| Instruction  | 2 4 0 0 |          |          |

|--------------|---------|----------|----------|

| Before Input | 0 0 6   | 00000000 | 00000011 |

| After Input  | 0 0 6   | 80000003 | 00000011 |

Input from Device 1, No Parity Error

| Instruction  | 2 2 0 0 |          |          |

|--------------|---------|----------|----------|

| Before Input | 0 0 6   | 012W67X3 | 00010011 |

| After Input  | 0 0 6   | 00000003 | 00000011 |

|                |             |                       |

|----------------|-------------|-----------------------|

| <u>Command</u> | FA 5 Output | Unknown.              |

| <u>Code</u>    | S 0 7 X     | No Device. Clear FA 5 |

|                | S 2 7 X     | Device 1              |

|                | S 4 7 X     | Device 2              |

|                | S 6 7 X     | Device 1 and 2        |

|                | S 8 7 X     | Device 3              |

|                | S S 7 X     | Device 1 and 3        |

|                | S U 7 X     | Device 2 and 3        |

|                | S W 7 X     | Device 1, 2, and 3.   |

#### Instruction

S B 7 X      B = 0, 2, 4, 6, 8, S, U, W.

#### Fast Access Registers

0 0 5

#### Description

The FA 5 output command takes the low order two tetrads (T0, T1) of fast access register 5 and sends them to the device or devices specified by the T2 tetrad of the instruction. The command then sets the contents of FA 5 to zero. The character read out of the computer has its bits rearranged by the command to 876P4321 from the internal format of 8P764321. The computer automatically computes a parity bit for output if the T1-4 bit of the two tetrads is zero. A parity bit of one will be inserted into the character if the sum of the bits is even; if the sum of the bits is odd, a zero will be inserted. However, if the T1-4 bit is equal to one, a one is always inserted into the parity bit position on output.

If the output device or devices that the output character is sent to are not ready or available to receive the character, the computer will wait at these devices holding the character until the device or devices are ready or available. No other computer operation will proceed until the output command has been executed.

Example

Output to Devices 2 and 3

| Instruction   | S U 7 X         |                    |                                        |

|---------------|-----------------|--------------------|----------------------------------------|

|               | <u>Register</u> | <u>Sexadecimal</u> | <u>Binary Character Representation</u> |

| Before Output | 0 0 5           | 00000013           | 00010011                               |

| After Output  | 0 0 5           | 00000000           | 00100011                               |

Output to Devices 1, 2, and 3

| Instruction   | S W 7 X         |                    |                                        |

|---------------|-----------------|--------------------|----------------------------------------|

|               | <u>Register</u> | <u>Sexadecimal</u> | <u>Binary Character Representation</u> |

| Before Output | 0 0 5           | 00000041           | 01000001                               |

| After Output  | 0 0 5           | 00000000           | 00010001                               |

| <u>Command</u>     | <u>Instruction Output Known.</u> |                                          |

|--------------------|----------------------------------|------------------------------------------|

| <u>Code</u>        |                                  |                                          |

| S 3 - -            | Device 1                         |                                          |

| S 5 - -            | Device 2                         | TAPE. output                             |

| S 7 - -            | Device 1 and 2                   |                                          |

| S 9 - -            | Device 3                         |                                          |

| S T - -            | Device 1 and 3                   |                                          |

| S V - -            | Device 2 and 3                   |                                          |

| S X - -            | Device 1, 2, and 3               |                                          |

| <u>Instruction</u> | S P C C                          | P = 3, 5, 7, 9, T, V, X<br>CC = 0 0 → XX |

### Fast Access Registers

None

### Description

The instruction output command takes the T0 and T1 tetrads of the instruction and sends them to the output devices specified by the P tetrad where they become output characters. The format of the output character is rearranged automatically on output from 8P764321 within the instruction to 876P4321 when actually sent to the output device. Parity is not computed for this output; however, the programmer can assign parity by making the P position equal to one if the sum of the other character bits is even. The P position should be zero if the sum of the remaining bits is odd.

If the output device or devices that the output character is sent to are not ready or available to receive the character, the computer will wait at these devices holding the character until the device or devices are ready or available. No other computer operations can proceed until the instruction output command is executed.

### Example

#### Output to Device 1

| <u>Instruction</u> | S 3 6 2 | <u>Register</u> | <u>Binary Character Representation</u> |

|--------------------|---------|-----------------|----------------------------------------|

| Before Output      | None    |                 | 01100010                               |

| After Output       | None    |                 | 01010010                               |

**Output to Device 1 and 2**

| <b>Instruction</b> | <b>S 7 0 1</b>  | <b>Binary Character Representation</b> |

|--------------------|-----------------|----------------------------------------|

|                    | <u>Register</u> |                                        |

| Before Output      | None            | 00000001                               |

| After Output       | None            | 00000001                               |

## SHIFT COMMANDS

### General

The Monrobot Mark XI has six types of shift commands. These commands are designed to shift data and to aid in the binary-decimal conversions. These shift commands, which will be described in detail below, are:

- (1) Decimal Shift Left (multiply by  $10^1$  to  $10^8$ ).

- (2) Decimal Shift Right (divide by  $10^1$  to  $10^8$ ).

- (3) Binary Shift Left (multiply by  $2^1$  to  $2^8$ ).

- (4) Binary Shift Right (divide by  $2^1$  to  $2^8$ ).

- (5) Binary Left End Around Shift (multiply FA 6 and FA 5 by  $2^1$  to  $2^8$ ).

- (6) Binary Shift Right Maintain High Order Bits (divide positive or negative by  $2^1$  to  $2^8$ ).

The shift commands always operate on the contents of FA 6 (accumulator) and also in one case (binary left end around shift) FA 5. Consequently, each shift instruction has the following form

|         |   |    |   |                  |    |   |   |    |   |   |   |   |   |   |   |

|---------|---|----|---|------------------|----|---|---|----|---|---|---|---|---|---|---|

| 8       | 4 | 2  | 1 | 8                | 4  | 2 | 1 | 8  | 4 | 2 | 1 | 8 | 4 | 2 | 1 |

| T3      |   | T2 |   |                  | T1 |   |   | T0 |   |   |   |   |   |   |   |

| Command |   |    |   | Number of Shifts |    |   |   |    |   |   |   |   |   |   |   |

where the T3 and T2 tetrads give the command code for the type of shift and the T1 and T0 tetrads give the power ( $n^1$  to  $n^8$ ) by which the information is to be shifted.

The sexadecimal coding for each shift command is given in Table 3. The sexadecimal coding for the number of shifts desired is given in Table 4. A shift of zero units is not permissible. If this shift is coded, the computer will cycle endlessly until operator intervention resets the computer.

The sign of numeric data is not preserved by the shift instructions with the exception of the binary shift right maintain high order bits. The sign bit position (T7-8) in FA 6 is shifted by these commands exactly as all the other bit positions.

Shift Command Coding